# SCI7654M0A/C0A

# **DC/DC Converter**

- Double/Triple/Quadruple Boosting

- 95% Excellent Power Conversion Efficiency

- Built-in Voltage Regulator

#### **■** DESCRIPTION

The SCI7654 is a highly efficient, but low power-consumption DC-to-DC converter based on the advanced CMOS technologies. It can generate an output voltage double/triple/quadruple times higher than the input (in negative direction) if 4/3/2 external capacitors are attached.

With a built-in voltage regulator, the SCI7654 can provide a stable output by setting the DC/DC output to any voltage via two external resistors. This is optimum to the LCD panel power supply as the stable output can have the negative temperature gradient required for an LCD panel.

#### **FEATURES**

- An input voltage can be boosted double/triple/quadruple to negative potential.

- Input voltages: -2.4 to -5.5V (quadruple boosting), -2.4 to -7.3V (triple boosting), -2.4 to -11.0V (double boosting)

- Excellent vol tage conversion efficiency: 95% (Typ.)

- Large output current: 20 mA (Max.) during quadruple boosting

- Built-in voltage regulator (for stable voltage output)

- Built-in reference voltage source for accurate regulation: -1.5 ±0.05V (CT0)

- Regulator output voltage temperature gradient function: -0.04, -0.15, -0.35, -0.55%/°C

- Low current consumption: 130 μA (Typ.)

- Low standby current: 5.0 μA (Max.)

- Built-in oscillator circuit

- 5/6-time voltage boosting in negative potential by serial connection

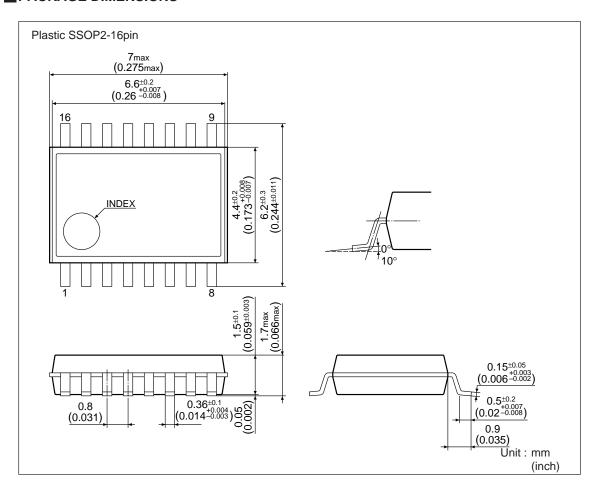

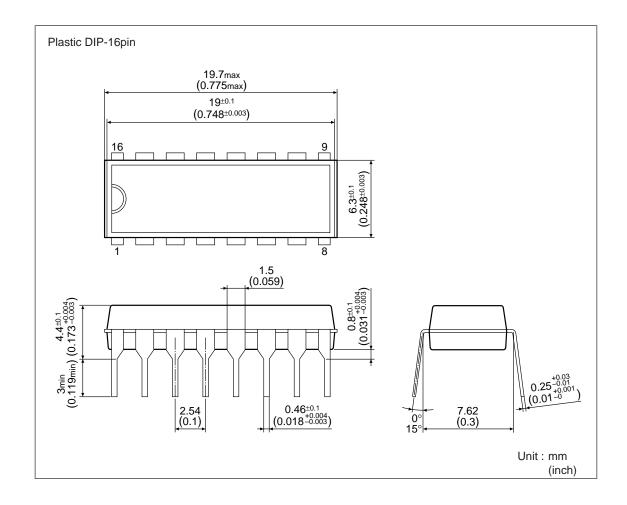

- Package: SCI7654MoA SSOP2-16pin (plastic), SCI7654CoA DIP-16pin (plastic)

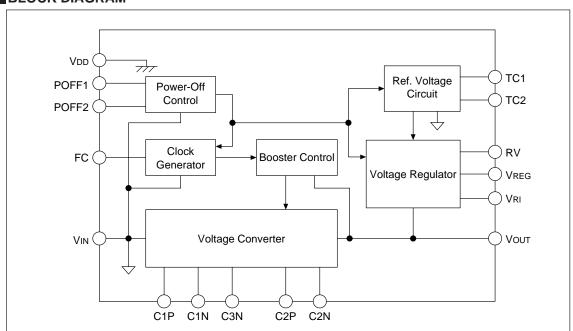

#### BLOCK DIAGRAM

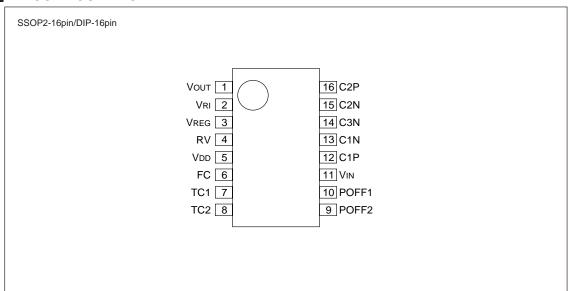

# PIN CONFIGURATION

# **PIN DESCRIPTION**

2

| Pin No. | Pin Name | Function                                                             |

|---------|----------|----------------------------------------------------------------------|

| 1       | Vout     | Voltage output                                                       |

| 2       | VRI      | Regulator input                                                      |

| 3       | VREG     | Regulator output                                                     |

| 4       | RV       | Input for regulator output voltage adjustment                        |

| 5       | VDD      | Input voltage pin (Positive)                                         |

| 6       | FC       | Internal clock rate switch input, and clock input in serial/parallel |

|         |          | connection (Common input pin)                                        |

| 7       | TC1      | Input for regulator output temperature gradient setup (1)            |

| 8       | TC2      | Input for regulator output temperature gradient setup (2)            |

| 9       | POFF2    | Power-off control input (2)                                          |

| 10      | POFF1    | Power-off control input (1)                                          |

| 11      | VIN      | Input voltage pin (Negative)                                         |

| 12      | C1P      | Common double and quadruple boosting capacitor positive pin          |

| 13      | C1N      | Double boosting capacitor negative pin                               |

| 14      | C3N      | Quadruple boosting capacitor negative pin                            |

| 15      | C2N      | Triple boosting capacitor negative pin                               |

| 16      | C2P      | Triple boosting capacitor positive pin                               |

# ■ ABSOLUTE MAXIMUM RATINGS

| Rating                         | Symbol                        | Min.         | Max.         | Unit | Remark                      |

|--------------------------------|-------------------------------|--------------|--------------|------|-----------------------------|

| Input Power Voltage            | VIN                           | -26.0/N      | VDD +0.3     | V    | N=Boosting time;            |

|                                |                               |              |              |      | at VIN pin                  |

| Input Pin Voltage              | Vı                            | Vin -0.3     | VDD +0.3     | V    | POFF1, POFF2                |

|                                |                               |              |              |      | TC1, TC2, FC pins           |

| Output Pin Voltage 1           | V <sub>0</sub> C <sub>1</sub> | Vin -0.3     | VDD +0.3     | V    | At C1P and C2P pins         |

| Output Pin Voltage 2           | Voc2                          | 2 × Vin -0.3 | Vin +0.3     | V    | At C1N pin                  |

| Output Pin Voltage 3           | Voc3                          | 3 × Vin -0.3 | 2 × Vin +0.3 | V    | At C2N pin                  |

| Output Pin Voltage 4           | Voc4                          | 4 × VIN -0.3 | 3 × Vin +0.3 | V    | At C3N pin                  |

| Regulator Input Power Voltage  | VrI                           | N × VIN -0.3 | VDD +0.3     | V    | N=Boosting time; at VRI pin |

| Regulator Input Pin Voltage    | VRV                           | N × VIN -0.3 | VDD +0.3     | V    | N=Boosting time; at RV pin  |

| Output Voltage                 | Vo                            | N × VIN -0.3 | VDD +0.3     | V    | N=Boosting time; at Vout    |

|                                |                               |              |              |      | and VREG pins               |

| Input Current                  | lin                           | _            | 80           | mA   | At VIN pin                  |

| Output Current                 | Іоит                          | _            | N≤4: 20      | mA   | N=Boosting time; at Vout    |

|                                |                               |              | N>4: 80/N    |      | and VREG pins               |

| Allowable Loss                 | Pd                            | _            | 210          | mW   | _                           |

| Operating Temperature          | Topr                          | -30          | 85           | °C   | _                           |

| Storage Temperature            | Tstg                          | -55          | 150          | °C   | _                           |

| Soldering Temperature and Time | Tsol                          | _            | 260•10       | °C·S | Temperature at leads        |

# **ELECTRICAL CHARACTERISTICS**

(Unless otherwise designated: Ta= $-30^{\circ}$ V to +85°C, VDD=0V, VIN=-5.0V)

| Characteristic                                 | Symbol | Condition                                                                       | Min.  | Тур. | Max. | Unit |

|------------------------------------------------|--------|---------------------------------------------------------------------------------|-------|------|------|------|

| Input Power Voltage 1                          | VIN1   | During quadruple boosting                                                       | -5.5  | _    | -2.4 | V    |

| Input Power Voltage 2                          | VIN2   | During triple boosting                                                          | -7.3  | _    | -2.4 | V    |

| Input Power Voltage 3                          | VIN3   | During double boosting                                                          | -11   |      | -2.4 | V    |

| Input Power Voltage N                          | VINN   | During large-time boosting using external diodes                                | -22/N | _    | -2.4 | V    |

| Boost Startup Input Power Voltage              | VSTA   | N=Boosting time, Ioυτ<200 μA, FC=VDD                                            | -22/N | _    | -2.4 | V    |

| Booster Output Voltage                         | Vout   | _                                                                               | -22   | _    | _    | V    |

| Regulator Input Voltage                        | VRI    | _                                                                               | -22   | _    | -2.4 | V    |

| Regulator Output Voltage                       | VREG   | IREG=0, VRI=-22V,                                                               | _     | _    | -2.4 | V    |

|                                                |        | Rrv=1MΩ                                                                         |       |      |      |      |

| Booster Output Impedance                       | Rout   | IOUT=10mA, during quadruple boosting                                            | _     | 200  | 300  | Ω    |

| Booster Power Conversion<br>Efficiency         | Peff   | IOUT=2 mA; during quadruple boosting; C1, C2, C3, COUT=10μF Tantalum            | _     | 95   | _    | %    |

| Booster Operating Current Ion<br>Consumption 1 |        | FC=VDD, POFF1=VIN, POFF2=VDD; during no loading; C1, C2, C3, COUT=10μF Tantalum | _     | 130  | 220  | μΑ   |

| Booster Operating Current<br>Consumption 2     | IOPR2  | FC=VIN, POFF1=VIN, POFF2=VDD; during no loading; C1, C2, C3, COUT=10μF Tantalum | _     | 520  | 880  | μΑ   |

| Regulator Operating Current<br>Consumption     | IOPVR  | $V_{RI=-20}$ V, during no loading, $R_{RV=1}$ $M\Omega$                         | _     | 10   | 15   | μΑ   |

# **■ ELECTRICAL CHARACTERISTICS (continued)**

| Characteristic                    | Symbol          | Condition                                                                                  | Min.   | Тур.  | Max.   | Unit |

|-----------------------------------|-----------------|--------------------------------------------------------------------------------------------|--------|-------|--------|------|

| Static Current                    | IQ              | POFF1=Vin, POFF2=Vin, FC=Vdd                                                               | _      | _     | 5.0    | μΑ   |

| Input Leakage Current ILIN        |                 | At POFF1, POFF2, FC, TC1, TC2 pins                                                         | _      | _     | 0.5    | μΑ   |

| Stable Output Saturation          | RSAT            | 0 <ireg<20ma< td=""><td>_</td><td>10</td><td>20</td><td>Ω</td></ireg<20ma<>                | _      | 10    | 20     | Ω    |

| Resistance                        | (*1)            | RV=VDD                                                                                     |        |       |        |      |

|                                   |                 | Ta=25°C                                                                                    |        |       |        |      |

| Stable Output Voltage Stability   | DVR             | -20V <vri<-10v, ireg="1mA&lt;/td"><td>_</td><td>0.2</td><td>_</td><td>%/V</td></vri<-10v,> | _      | 0.2   | _      | %/V  |

|                                   | (*2)            | VREG=-15V                                                                                  |        |       |        |      |

|                                   |                 | Ta=25°C                                                                                    |        |       |        |      |

| Stable Output Load Variation      | DV <sub>0</sub> | VRI=-20V VREG=-15V                                                                         | _      | 30    | 50     | mV   |

|                                   | (*3)            | Ta=25°C                                                                                    |        |       |        |      |

|                                   |                 | 0 <ireg<20ma< td=""><td></td><td></td><td></td><td></td></ireg<20ma<>                      |        |       |        |      |

| Reference Voltage                 | VREF0           | TC1 = VDD, TC2 = VDD                                                                       | -1.55  | -1.50 | -1.45  | V    |

| (Ta = 25°C)                       | VREF1           | TC1 = VDD, TC2 = VIN                                                                       | -1.70  | -1.50 | -1.30  | V    |

|                                   | VREF2           | TC1 = VIN, TC2 = VDD                                                                       | -1.90  | -1.50 | -1.10  | V    |

|                                   | VREF3           | TC1 = VIN, TC2 = VIN                                                                       | -2.15  | -1.50 | -0.85  | V    |

| Reference Voltage Temperature     | CT <sub>0</sub> | TC1 = VDD, TC2 = VDD, SSO package                                                          | -0.07  | -0.04 | 0      | %/°C |

| Coefficient (*4)                  | CT1             | TC1 = VDD, TC2 = VIN, SSO package                                                          | -0.25  | -0.15 | -0.07  | %/°C |

| (*5)                              | CT2             | TC1 = VIN, TC2 = VDD, SSO package                                                          | -0.45  | -0.35 | -0.20  | %/°C |

|                                   | СТз             | TC1 = VIN, TC2 = VIN, SSO package                                                          | -0.75  | -0.55 | -0.30  | %/°C |

|                                   | VIH             | VIN =-2.0V to -5.5V                                                                        |        |       |        |      |

|                                   |                 | At POFF1, POFF2, FC, TC1,                                                                  | 0.2VIN | _     | _      | V    |

| Input Voltage Level               |                 | TC2 pins                                                                                   |        |       |        |      |

| Input voltage Level               | VIL             | VIN =-2.0V to -5.5V                                                                        |        |       |        |      |

|                                   |                 | At POFF1, POFF2, FC, TC1,                                                                  | _      | _     | 0.8VIN | V    |

|                                   |                 | TC2 pins                                                                                   |        |       |        |      |

| Capacitance of Booster Capacitors | Смах            | Capacitors                                                                                 | _      | _     | 47     | μF   |

|                                   |                 | C1, C2, C3                                                                                 |        |       |        |      |

(\*1) RSAT =

$$\frac{\Delta(VREG - VOUT)}{\Delta IREG}$$

(\*2) VR =

$$\frac{\Delta VREG}{\Delta VOUT \cdot VREG}$$

(\*3) R0 =

$$\frac{\Delta V_{REG}}{\Delta I_{REG}}$$

(\*4) CT =

$$\frac{|VREF(50^{\circ}C)| - |VREF(0^{\circ}C)|}{50^{\circ}C - 0^{\circ}C} \times \frac{100}{|VREF(25^{\circ}C)|}$$

(\*5) The reference voltage temperature coefficient of each chip product may vary depending on the used molding materials. Perform the temperature test before use.

#### ■ FUNCTIONAL DESCRIPTION

#### Clock Generator Circuit

As the SCI7654 has a built-in clock generator circuit, it requires no external source at all. The clock rate changes depending on the FC pin signal level, and the Low Output or High Output mode can be selected. This allows a frequency selection according to the current capacitance and load current when the booster output impedance changes depending on the clock rate and external booster capacitance.

| FC pin  | Mode        | Clock Rate Current Consumption |                        | Output Ripple           |  |

|---------|-------------|--------------------------------|------------------------|-------------------------|--|

| H (VDD) | Low Output  | 4.0 kHz (Typ.)                 | ЮР                     | VRP                     |  |

| L (VIN) | High Output | 16.0 kHz (Typ.)                | Approx. 4 times of IOP | Approx. 1/4 time of VRI |  |

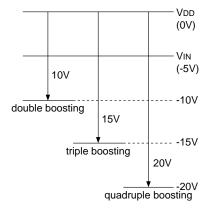

#### ● Voltage Converter Circuit

The voltage converter receives a clock from the clock generator, and boosts the VIN input power voltage quadruple, triple or double. Four converter circuits are required for quadruple boosting, three converts are required for triple boosting, and dual converters are required for double boosting.

Voltage step-up diagram (during -5V input)

#### ■ Reference Voltage Circuit

The SCI7654 has a built-in reference voltage circuit for the voltage regulator. The temperature coefficient of reference voltage can be changed using pins TC1 and TC2, and a voltage having one of four types of temperature gradients can be output at VREG pin for LCD driving.

|      | TC1    | TC2    | Reference Voltage, VREF (V) |      |       | Temperature Coefficient, CT (%/°C) |       |       |

|------|--------|--------|-----------------------------|------|-------|------------------------------------|-------|-------|

| Mode |        | 102    | Min.                        | Тур. | Max.  | Min.                               | Тур.  | Max.  |

| CT0  | H(VDD) | H(VDD) | -1.55                       | -1.5 | -1.45 | -0.07                              | -0.04 | 0     |

| CT1  | Н      | L(VIN) | -1.70                       | -1.5 | -1.30 | -0.25                              | -0.15 | -0.07 |

| CT2  | L(VIN) | Н      | -1.90                       | -1.5 | -1.10 | -0.45                              | -0.35 | -0.20 |

| CT3  | L      | L      | -2.15                       | -1.5 | -0.85 | -0.75                              | -0.55 | -0.30 |

# SCI7654M0A/C0A

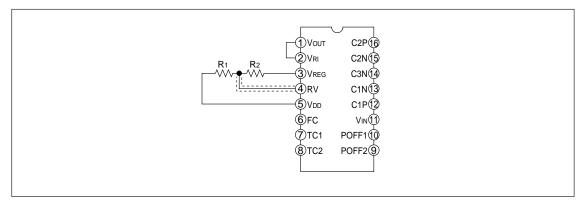

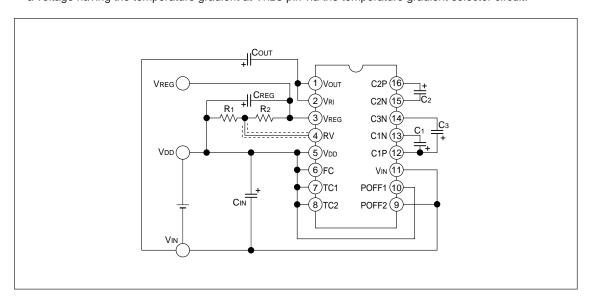

# ■ Voltage Regulator Circuit

The circuit receives a voltage from VRI pin, stabilizes it, and outputs at any voltage. The output is adjustable with a ratio of R1 and R2 external divider resistors. Although the sum of divider resistors is desirable to be minimum to prevent an interference due to external noise, 100 to 1 megohms are recommended as the current consumption may be increased by the divider resistors.

#### ■ Power Off Control

The SCI7654 has an automatic power-off function, and can turn on or off each function depending on the external signals entered in POFF1 and POFF2 pins.

|      | POFF1  | POFF2  | Function Status |          |           |                                     |  |  |

|------|--------|--------|-----------------|----------|-----------|-------------------------------------|--|--|

| Mode | FOLL   | FOITZ  | Oscillator      | Booster  | Regulator | Description                         |  |  |

| PS1  | H(VDD) | L(VIN) | ON              | ON       | ON        | All circuits are turned ON.         |  |  |

| PS2  | L      | L      | OFF             | OFF (*1) | OFF (*2)  | All circuits are turned OFF.        |  |  |

| PS3  | Н      | Н      | OFF             | ON       | ON        | Slave side (booster and regulator)  |  |  |

|      |        |        |                 |          |           | in parallel connection              |  |  |

|      |        |        |                 |          |           | Master side (for booster only)      |  |  |

| PS4  | L      | Н      | ON              | ON       | OFF       | in parallel connection; first stage |  |  |

|      |        |        |                 |          |           | in serial connection (*3)           |  |  |

<sup>\*1</sup> When the booster circuit is OFF, approximately VIN +0.6V voltage appears at VOUT pin.

EPSON

6

<sup>\*2</sup> When the regulator is OFF, the VREG pin is set to the high-impedance status.

<sup>\*3</sup> The mode selected depends on the line connection at the second stage of serial connection.

## REFERENCE CIRCUIT EXAMPLE

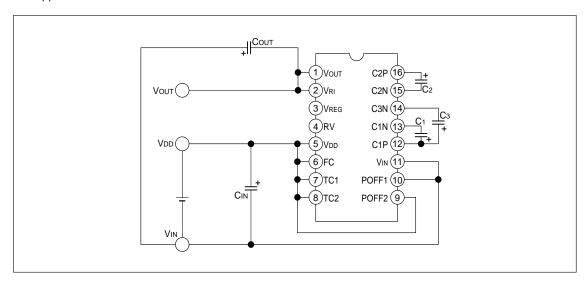

## ● Four-time booster circuit

This example drives the booster circuit only, boosts the VIN input voltage four times in negative direction, and outputs it at the VOUT pin. However, this does not have a voltage regulator and the voltage at VOUT pin may have a ripple.

## • Four-time booster and regulator circuits

This example receives a boost output from VouT pin, stabilizes it via the voltage regulator circuit, and outputs a voltage having the temperature gradient at VREG pin via the temperature gradient selector circuit.

# **PACKAGE DIMENSIONS**

#### NOTICE:

No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as, medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. This material or portions thereof may contain technology or the subject relating to strategic products under the control of the Foreign Exchange and Foreign Trade Law of Japan and may require an export license from the Ministry of International Trade and Industry or other approval from another government agency.

© Seiko Epson Corporation 2000 All right reserved.

All other product names mentioned herein are trademarks and/or registered trademarks of their respective companies.

#### **SEIKO EPSON CORPORATION**

[ELECTRONIC DEVICES MARKETING DIVISION]

IC Marketing & Engineering Group

**ED International Marketing Department I (Europe & U.S.A.)** 421-8, Hino, Hino-shi, Tokyo 191-8501, JAPAN Phone: +81-(0)42-587-5812 FAX: +81-(0)42-587-5564

ED International Marketing Department II (Asia) 421-8, Hino, Hino-shi, Tokyo 191-8501, JAPAN

421-8, Hino, Hino-sni, Tokyo 191-8501, JAPAN Phone: +81-(0)42-587-5814 FAX: +81-(0)42-587-5110 ■ EPSON Electronic Devices Website http://www.epson.co.jp/device/

First issue June, 1995 Printed February, 2000 in Japan T